Ogni progettista, hardware o software, sa benissimo che ogni fase del suo lavoro esiste uno strumento di lavoro dedicato.

Ogni progettista, hardware o software, sa benissimo che ogni fase del suo lavoro esiste uno strumento di lavoro dedicato.

Quando parliamo di problemi software sappiamo che per descrivere, in forma algoritmica, il nostro lavoro dobbiamo ricorrere a un linguaggio propriamente software, per esempio C o Basic.

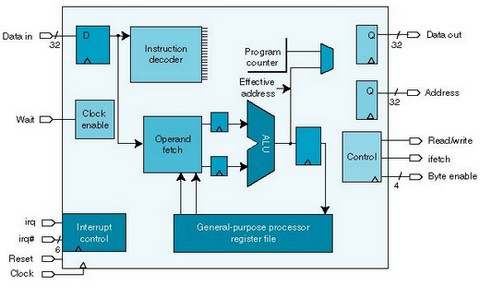

Per la stessa ragione, un progettista hardware ha l’esigenza, non di descrivere in forma algoritmica, ma di modellare un circuito o schema elettrico che sia questo complesso o meno. Per fare questo lavoro ricorre a un linguaggio che rientra nella famiglia HDL (o Hardware Description Language).

Rientrano in questa famiglia linguaggi quali VHDL o Verilog. Un linguaggio HDL non ha l’obiettivo di rendere eseguibile un programma, così come farebbe un progettista software, ma semmai si preoccuperebbe di renderlo simulabile. Quando parliamo di programma HDL ci vogliamo riferire alla descrizione di uno schema elettrico, di un circuito o di un integrato.